PCIe-DIO-24DCS, PCI Express Digital I/O Card w/Counters and CoS Detection

Features

- 24 high-current DIO lines

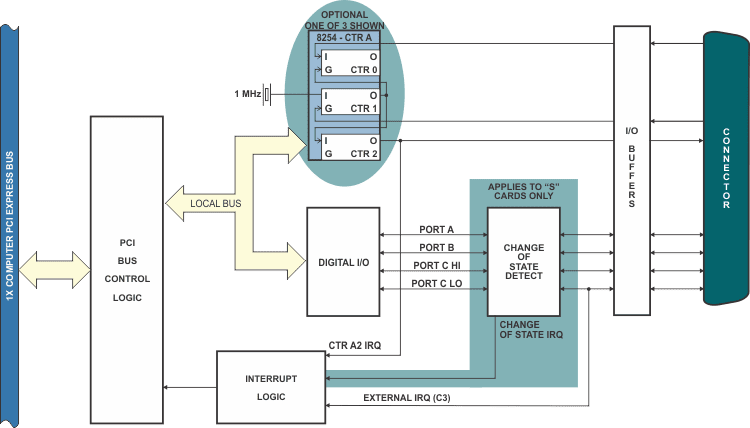

- Three optional 82C54 Counter / Timers

- IRQ generation from Port C bit 3, and Counter A2 (“C” models) and/or Change-of-State (COS) Detection (“S” models)

- “S” models now include Digital Integration Features

- 8 bits with Edge-selectable Event Counting, Pulse Width and PWM measurement, and per-bit Edge-selectable CoS IRQs

- 8 bits with Pulse Train (“generate n pulses”) and PWM generation

- Four and eight bit ports independently selectable for inputs or outputs

- Software selectable 10k ohm Pull-up/Pulldown resistors on DIO lines

- Jumper selectable VCCIO (5V, 3.3V, 2.5V,1.8V)

- VCCIO voltage available to the user via 0.5A resettable fuse

- Designed, made, supported, and manufactured in the USA

FACTORY OPTIONS

- Extended temperature operation (-40° to +85°C)

- RoHS compliant version

- Support for Wind River VxWorks (call for ordering information)

$229.00 – $299.00

In StockDescription

PCI Express Digital I/O Cards with Counters and COS Detection

This product is an x1 lane PCIe DIO board available in four models ranging from basic DIO to advanced COS detection and Counter/Timer capabilities. The card emulates an 8255 compatible chip, providing 24 DIO lines. The DIO lines are grouped into three 8-bit ports: A, B, and C. Each 8-bit port is configured via software to function as either inputs or outputs. Port C can be further broken into two 4-bit nybbles via software and configured as either inputs or outputs.

Each DIO line is buffered and capable of up to 32mA source/sink. The VCCIO logic level is globally configured via jumper selection as 5V, 3.3V, 2.5V or 1.8V. Also, ports A, B, C low nybble, and C high nybble are individually software selected as pull-up or pull-down through 10kΩ resistor networks. The last configured pull-up/down state is stored in on-board non-volatile memory and automatically applied at the next power up. The board is shipped factory default as pulled-up.

The card is 6.6 inches in length and 4.2 inches seated height. I/O wiring connections for this board are via a male 37-pin D-sub connector. A ribbon cable can be used to connect this card to termination panels.

Digital ∫ Features

“S” Models include new Digital Integration Features on 8 bits of input and 8 bits of output.

- Inputs: Enhanced Change-of-State IRQs can be enabled on a bit-by-bit basis, with a selectable (rising/falling) edge. Separately enabled per-bit edges are counted with an optional overflow IRQ. Low-side and high-side pulse widths are measured with a resolution as fine as 8ns. These measurements automatically provide both frequency and duty cycle measurements for waveforms up to 65.5 MHz.

- Outputs: Individual rising-or-falling pulses can be generated, individually or simultaneously on up to 8 output bits, with durations controllable with 8ns resolution. Sequential pulses or continuous frequencies (with programmable duty-cycle) can also be output.

- EZUpdate: FPGA supports EZUpdate allowing new FPGA code to be written via software across the PCI Express bus, allowing field upgrade with new features.

For details regarding Digital Integration Features please refer to the Digital Integration Features Reference.

SOFTWARE

The card is supported for use in most operating systems and includes a free DOS, Linux, and Windows XP -> 10, both 32 & 64 bit compatible software package. This package contains sample programs and source code in Visual Basic, Delphi, and Visual C++ for Windows. Also provided is a graphical setup program in Windows. Linux support includes installation files and basic samples for programming from user level via an open source kernel driver. Third party support includes a Windows standard DLL interface usable from the most popular application programs. Embedded OS support includes Windows Xpe, WES7, vxWorks, etc.

Downloads

Data Sheets

Manuals

- PCIe-DIO-24DCS Family Manual

- Digital Integration Features Register Reference

- AIOWDM Software Reference Manual (.html)

Software

- PCIe-DIO-24DCS Family Software Package (Last Updated 2025-05-20)

Drivers and Downloads

Full list of available Downloads: Software Packages, Drivers, Manuals, and other documents

Information about our Free Software packages:

ACCES is proud to provide a full suite of software support with every Data Acquisition product. We are committed to supporting the most popular operating systems and platforms for our customers. Currently we are actively supporting 7 -> 11, both 32 & 64 bit, including “Server 2008,” “Embedded,” and “Compact” flavors for all plug-and-play products including PCI, PCI Express, USB, and more. Many products continue to ship with support for additional operating systems such as DOS, Windows 95, 98, Me, NT4, 2000, and XP.

Samples

Among the software we deliver with our products are sample programs in a wide variety of programming languages. These samples are used to demonstrate the software interfaces to our products — and many can be used as-is in your production environments, or to test functionality of the devices out-of-the-box. We’re currently actively supporting sample programs in Microsoft Visual C#, and Delphi, with many devices including samples in Visual Basic (5 and .NET), Visual C/C++, and Borland C/C++ 3.1 for DOS. Additionally we provide National Instruments LabVIEW compatible DLLs and many demonstration VIs for our devices.

Drivers

Drivers for various operating systems are also provided, including active support for Windows 7 -> 11 — all in both 32-bit and 64-bit flavors, and including consumer, server, and embedded varieties — as well as the 2.6 and newer Linux kernels and recent OSX / macOS versions. Many products continue to ship with driver support for Windows 95, 98, Me, NT4, Windows 2000, XP, and more, but support for these operating systems is considered deprecated.

Setup Programs and Utilities

Our Data Acquisition devices also include a graphical setup utility that walks you through the process of configuring any option jumpers or switches on the device, as well as explaining a little about the various connectors present.

Many devices also include utility programs – little tools to make your use of the device easier, such as EWriter, a program that allows you to read and write data in the user-accessible EEPROM locations on all our USB data acquisition products; or WinRISC, a “Really Incredibly Simple Communications” terminal program that lets you get started instantly with serial devices.

“Register Level” Documentation

Besides all this software in all these languages and operating systems ACCES has a policy of open and transparent development: none of our lowest-level “register” interfaces are hidden from you — we document every register in every bus card, every command in every serial board, and every usb control transfer in every USB Data Acquisition board. These lowest-level interfaces allow you to develop for our products in ANY operating system or language, regardless of our actively supporting it or having a driver for it. We have customers actively developing in ADA, Android, Python, Java, MATLAB, Solaris, and more, just by referring to our complete low-level interface documentation! And we provide the full source code to all of our drivers, regardless of operating system, to give you an even bigger head start in your own development tasks.

No Fees or Royalties

All of this software is provided at no additional charge, and is licensed under any of a variety of flexible — and royalty free — options. Check out our software license explanation if you’d like more information.

Custom Software

ACCES also offers Custom Software Services for our products. Our prices are unbelievably low, often as inexpensive as free! If you need something tweaked to support your needs, or an entire enterprise application developed from scratch, it is definitely worth your time to inquire with us, first.

Further information about available ACCES Software:

Redistributing Windows Drivers

A list of ACCES drivers and the files that compose them under different versions of Windows, so you can easily redistribute ACCES cards and drivers.

aioWDM.VxWorks

ACCES has successfully partnered with Wind River to bring our entire line of PCI and PCI Express DAQ cards to VxWorks 7!

VxWorks 7 VxBus Gen 2 drivers, with easy-to-use API-libraries, are available for this product, including full source and sample code.

Designed to be compatible with our AIOWDM.dll Windows driver & API, this kernel module adds zero% CPU-cycle overhead to your VxWorks runtimes while allowing the lowest-latency hardware register access possible.

You can find more information about our VxWorks libraries and services on our Wind River Silver Partner page.

Digital I/O

Logic Levels

- 5 Volt

- Input Low ≤ 1.5V, ≤2µA

- Input High ≥3.5V, ≤2µA

- Output Low ≤ 0.55V @ 32mA

- Output High ≥3.8V @ 32mA

- 3.3V

- Input Low ≤ 0.8V, ≤2µA

- Input High ≥2.0V, ≤2µA

- Output Low ≤ 0.55V @ 24mA

- Output High ≥2.4V @ 24mA

- 2.5V

- Input Low ≤ 0.7V, ≤2µA

- Input High ≥1.7V, ≤2µA

- Output Low ≤ 0.3V @ 8mA

- Output High ≥1.9V @ 8mA

- 1.8V

- Input Low ≤ 0.63V, ≤2µA

- Input High ≥1.17V, ≤2µA

- Output Low ≤ 0.45V @ 4mA

- Output High ≥1.2V @ 4mA

Counter / Timers

- Number / Type Three 82C54 programmable counters

- Counter size 16-bit

- Logic level VCCIO

- On-board clock 1MHz

- Clock Pulse Width High – 30ns (min) Low – 40ns (min)

Environmental

- Operating Temperature 0° to 70°C, optional -40° to +85°C

- Storage Temperature -55° to +150°C

- Humidity 5% to 90% RH, w/o condensation

- Card Dimensions Length – 6.6″; Height – 4.2″ seated

Regulatory Compliance

This product is in full compliance with CE requirements.

| Model | Description | Price (USD) | |

|---|---|---|---|

| PCIe-DIO-24DCS | PCI Express 24 DIO Card with 3 Counters and CoS Detection | $299.00 | |

| PCIe-DIO-24DC | PCI Express 24 DIO Card with 3 Counters | $279.00 | |

| PCIe-DIO-24DS | PCI Express 24 DIO Card with CoS Detection | $239.00 | |

| PCIe-DIO-24D | PCI Express 24 DIO Card | $229.00 |

| Accessories | |

|---|---|

| Direct Connect Terminals | |

| ADAP37F-MINI | Screw terminal adapter with a DB37F connector for direct mounting $40 |

| Cable Connectivity | |

| CAB37-18 | Ribbon cable, 37-pin connectors on each end, 18 inches long $25 |

| CAB37-xx | As above except “xx” equals length in inches (add $2 per Ft over 18″) $25 |

| STB-37 | DIN-rail mountable screw terminal board for 37-pin connector $39 |

| STA-37 | Screw terminal assembly with DB37F and DB37M connectors and breadboard area $79 |

| Hardware | |

| DIN-SNAP-6 | 6-inch SNAP-TRACK with two clips for mounting one STB-37 on a DIN rail $15 |

| T-BOX | Steel enclosure with powder coated finish, use to mount STA-37 to panel $45 |

| Model Options: | |

| -RoHS | RoHS compliant version |

| -T | Extended temperature (-40°C to +85°C) |